Los módulos de memoria DDR5 para servidores, que la empresa coreana SK Hynix desarrolló en colaboración con Intel y Renesas, deberían proporcionar tasas de transferencia de datos un 66 por ciento más altas por canal de memoria. Se utilizan chips de memoria SDRAM DDR5 comunes de la clase de velocidad DDR5-4800. Combinados en un DIMM registrado (RDIMM) para servidores, estos chips entregan un total de 38,4 gigabytes de datos por segundo (38,4 GB/s).

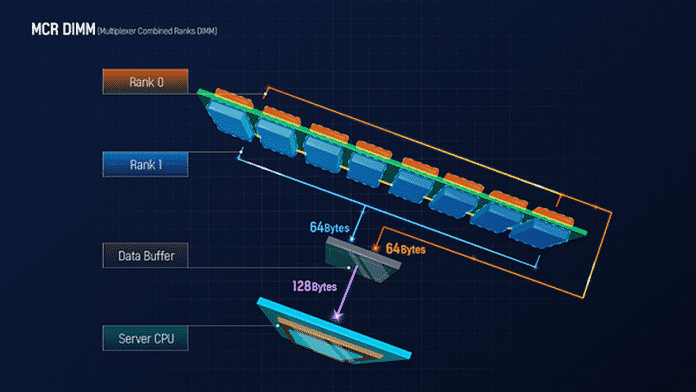

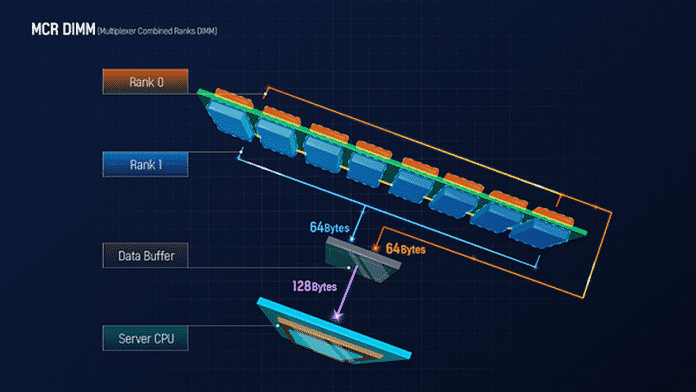

Sin embargo, gracias a un truco llamado rangos integrados de multiplexor (MCR), los MCR RDIMM ofrecen al menos dos rangos de tasas de transferencia de datos más altas, siempre que el controlador de memoria sea compatible con la tecnología MCR. Un chip de búfer adicional (intermedio/multiplexor) en el RDIMM distribuye los accesos a dos rangos cada uno y luego los envía al controlador de memoria a una tasa de señal más alta a través del canal de memoria.

Según SK Hynix, el búfer MCR desarrollado por Renesas logra velocidades de señal de hasta 8 giga de transferencias por segundo, lo que corresponde a DDR5-8000 o 64 GB/s en el canal de memoria.

Básicamente, la tecnología MCR continúa con el concepto básico de «pedido anticipado» externo, que se ha utilizado durante años dentro de DDR-RAM: varios bancos (banks) funcionan en paralelo dentro de los chips SDRAM. Los multiplexores de E/S en SDRAM transmiten estos datos secuencialmente a través del canal de memoria. También funciona en la dirección opuesta al escribir datos en celdas de memoria DRAM.

Cliente de rango y archivo

En el caso de los módulos de memoria (módulos de memoria dual en línea, DIMM), la matriz es un grupo de chips DRAM con 64 líneas de señal de datos: es decir, ocho chips x8 individuales con ocho líneas cada uno, o 16 chips x4, o cuatro chips x16. Solo se permiten chips x4 o x8 en RDIMM compatibles con JEDEC. Los RDIMM ECC para servidores con código de corrección de errores tienen chips DRAM adicionales para proteger contra errores de bits; Para DDR5 RDIMM, dos por rango.

Incluso con DDR5 RDIMM normales, las clasificaciones individuales no son mutuamente excluyentes; El controlador de memoria especifica el rango deseado a través de la señal de selección de chip (CS#). Con MCR RDIMM, el BIOS y el controlador de memoria deben asignar direcciones de RAM físicas de una manera más inteligente. Esto se debe a que la tecnología MCR no puede acelerar el acceso continuo en el mismo rango.

El búfer en el MCR-DIMM multiplexa las líneas de señal de datos de los dos rangos.

(Foto: SK Hynix)

¿Qué Jeon puede hacer MCR?

Al anunciar los DDR5 MCR RDIMM, SK Hynix no reveló qué próximos procesadores de servidor de Intel son capaces de tecnología MCR. Sin embargo, el 10 de enero de 2023, Intel anunció la presentación del procesador escalable Xeon Gen4 «Sapphire Rapids», significativamente retrasado. Esta generación de Xeon SP ejecutará ocho canales de RAM DDR5; El AMD Epyc 9004 «Genoa» de la competencia, por otro lado, tiene doce.

Sin embargo, el Xeon SP Gen4 está disponible como «Xeon Max» con memoria de alto ancho de banda (HBM) de alta velocidad directamente en la carcasa de la CPU. HBM funciona con DDR5 RDIMM y actúa como un búfer rápido (caché). AMD, a su vez, planea variantes de Genoa-X con un caché L3 apilado.

Ver también:

(Nota)

«Amante de los viajes extremos. Fanático del tocino. Alborotador. Introvertido. Apasionado fanático de la música».